簡易DC-DCコンバータ設計

ここではPICマイコンのPWMを使った簡易DC-DCコンバータの設計についてふれます。何が簡易かというと、フィードバックしていないオープンループ型だからです。従ってPICマイコンのPWMはフリーランしていて、ソフトで制御する必要はありません。 ニキシーの高圧など、定電圧化していなくても良い部分に使えます。PIC以外に必要なのは、パワーMOS FET、トランス、ダイオードと多少のCです。

せっかくなので、割と細かく記述します。

一番面倒なのがこれです。スイッチング電源用の標準トランスはまず見あたりません。商用電源と違い、設計周波数もマチマチだし、回路方式も色々ある、多出力ニーズが多いなど、標準として用意できるほど一般化できないので、通常は個別に設計して巻いてい るようです。

トランス設計で一番問題なのは、線を何回巻けば良いのかということだと思います。1次2次の電圧比と、巻線比が同じであるということはよく知られています。おそらくアマ無線の試験なんかにも出てくるパターンじゃないかと思います。しかしながら、絶対数として何回巻くのかという話は専門書でないと出てきません。 いきなり公式で出しても良いのですが、せっかくなので電磁気基礎の部分から誘導してみます。

まず、トランスコアのカタログを入手します。秋葉ラジオデパートのアイコー電子でTDKのコアが入手できるので、TDKのカタログを使います。

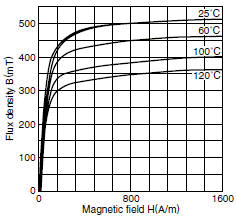

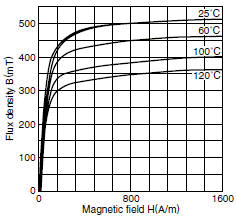

トランス設計に必要なデータは、コア にかけられる最大の磁束密度とサイズに関する情報で、TDKのカタログはこれらが別になっています。入手しやすいPC40材のコア特性が概要にのっています。 飽和磁束密度は25度で510mTと記してありますが、この値を設計上の最大磁束密度としてつかってはいけません。

下の図はカタログに示されたBH特性と呼ばれるもので す。まず、飽和磁束密度自体が温度でかなり変化することがわかります。加えて、肩特性は結構ブロードに変化しています。このグラフの傾きはコイル設計にきわめて重要な透磁率です。透磁率が設計通りとして使えそう(=傾きが一定と見なせる限界)は300-400mTではないでしょうか。今回は余裕をみて磁束密度=300mTで設計します。磁束密度は安全に関係し、飽和 すると過電流で事故になりますから余裕をもった設計が大事です。

次に、これも入手しやすいEI型のコアを使うため、Eコアから使用するコアの実効断面積を入手します。ここで、どのサイズのコアを使うかという問題になりますが、1−2W程度の小型電源であれば、 何でも良いです。EI16あたりが手頃なサイズかと思います。あまり小さいと巻きづらくなります。EI16コアの実効断面積は19.8mm2です。

ここからはかんたんな数式で巻数を出します。次の式をまとめれば、誘導できます。

![]() ... 磁束密度B、透磁率μ、起磁力H、巻数N、電流I、磁路長lの関係

。電磁気の基本の式です。

... 磁束密度B、透磁率μ、起磁力H、巻数N、電流I、磁路長lの関係

。電磁気の基本の式です。

![]() ...

叉交磁束密度Φの関係、ここでBの中にNがあるため、ΦはNの二乗に比例することがわかります。

...

叉交磁束密度Φの関係、ここでBの中にNがあるため、ΦはNの二乗に比例することがわかります。

これがハマルんですが、Φとφ、大文字は叉交磁束、小文字は磁束なんですよね。

![]() ...インダクタンスLの定義式

...インダクタンスLの定義式

![]() とします。これらをまとめてNの式にすると

、

とします。これらをまとめてNの式にすると

、

![]() となります。

となります。

これが求める巻数の式です。電磁気の教科書 ではコアの断面積をSとしていますが、実務系の本だとAeという名称になっているはずです。おそらく、apertureのAなんじゃないかと思います。eはeffectiveでしょう。

tは矩形波がONになっている時間なので、周波数fとデューティ比dで置き換えます。

![]()

最終的に次の式が得られ、電圧5V、周波数50kHz、デューティは50%、断面積19.8mm2、磁束密度300mTとすれば、1次側の巻数は![]()

8.4回となります。巻数は整数で、かつ上記の式で得られる巻数は最小の巻数なので、9回巻けば良いことになります。 2次側は巻数比で出しますので、仮に200Vがほしければ(200/5)×9=360回になります。 これでトランスの基本的な設計ができました。

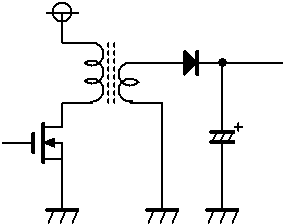

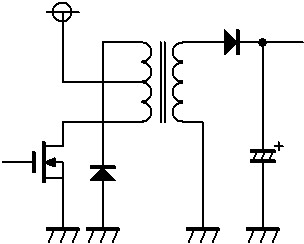

原理的回路

原理的回路では、1次側にPower MOS FETを入れてスイッチングさせ、2次側は単にダイオードとコンデンサで整流、平滑するだけです。これはおそらく、このままでは動きません。というのは、トランスに蓄積された「逆起電力」を逃がす回路が無いためで、発生する「逆起電力」でPower MOS FETが壊れると思います。

これについて少し考察してみます。原理回路は理想トランスでは動きます。理想トランスは直流をも変圧させ(つまり周波数完全フラット)、励磁インダクタンスが無限大 (励磁インダクタンスが無限大なので直流でも変圧できる)、損失もゼロというあり得ない理想素子です。ここで励磁インダクタンスというものが出てきました。これは1次側 コイルの自己インダクタンスのことです。上の式でLを求めている部分がありますが、これが励磁インダクタンスになります。1次巻数の2乗に比例しています。理想トランスに近づけるには、出来るだけ巻数を増やした方が良いことがわかりますが、労力の面と巻線の抵抗から生じる損失が出てきますので、トレードオフになります。実際には、コアの磁束密度の変位幅を最大使う設計=巻数最小をとります。

トランスの2次側を解放して考えると、1次側は単なるコイルそのものであって、当然ながら2次側の負荷状態に関係なく電流が流れます。この電流をトランスでは励磁電流と呼 びます。上の式でIを求めていますが、励磁インダクタンスに反比例、時間と電圧に比例します。

Power MOSがONのとき、 コイルに電流が流れ、エネルギが蓄積されます。

![]()

は高校の物理でも出てくる式だと思います。Power MOSがONからOFFに移るとき、磁束が減少に向かいますので2次側電圧は反転し、ダイオードは逆バイアスされるためトランスからみると2次側開放となります。一方、トランス1次側の電流は同じ向きに流れ続けようとしますので、Power MOSのドレイン側がプラス、電源VCC側がマイナスになる起電力が現れます。この電圧こそが逆起電力で、

![]()

となります。1次側の電流変化率(di/dt)に比例します。ここで急速にON->OFFと電流変化すると、きわめて高い電圧が出てきます。インダクションキックとも呼ばれる逆起電力は数百ボルトに達することがあります。こんな電圧がPower MOSにかかったら壊れてしまうということです。これを解決するための補助回路を組み入れる必要があります。

スナバー回路

スナバー回路というのは、スイッチに使うスパークキラーとほとんど同じで、過渡的なパワーを吸収(=熱に換える)するものです。トランスの1次側はPower MOSが電流を切ると、同じ向き、同じ大きさの電流を流し続けようとします。これをCRで吸収してしまいます。細かい設計は略しますが、だいたい1kΩと0.01uF程度で良いです。重要なのは、トランスが蓄積した電力をPower MOSがOFFになっている期間で全部吸収してしまう値とすることです。吸収できないと、トランスの磁束密度が下がりきらず、磁気飽和に至ります。出来るだけ高速に吸収するには高い抵抗値を選びます。高ければ良いというものではなく、高い抵抗にすると、キック電圧が上がりますのでPower MOSの定格から上限も決まってきます。

リセット回路

スナバーは電力をすべて熱に変換してしまいますので、電気の無駄であります。このトランスの励磁電力がどのくらいなのか計算してみます。

1周期での電力は

![]()

となります。lは磁路の長さ(34.6mm)、μは透磁率です。PC40コアの場合は2300ですが、これは比透磁率(μs)というもので、真空の透磁率(μ0)に対する比率ですから、μは実際には真空の透磁率と比透磁率の積を使います。(μ=μ0μs)

これで計算すると、約9.3×10-6Wとなります。周波数50kHzを掛けると、実に0.46Wにもなります。これだけの電力を無駄にはできないので、この電力を回収する補助回路をもうけます。トランス1次側に補助巻線 (リセット巻線)をもうけ、電源側のコンデンサに励磁電力を戻す方式で、これをリセット回路と呼びます。 (トランスの磁束を0に戻すということでリセットという名前ですが、前述のスナバーでも磁束を0にするという点は変わりません。)

リセット巻線は1次側と同じ巻数を巻きます。理由は省略しますが、この巻数がもっとも効率的になります。

この補助回路の動作は次のようになります。まず、Power MOSがターンONすると1次回路に電流が流れ、2次側に電圧が生じます。リセット巻線にも電圧が生じますが、リセット回路のダイオードは逆バイアスされますのでこの回路は動作しません。

Power MOSがターンOFFすると磁束が減少に転じます。すると、2次回路のダイオードは逆バイアスされますので動作しません。一方、リセット回路はダイオードが順バイアスされますので、電流が流れ、入力の電解コンデンサを充電します。 つまり、励磁電力はコンデンサに戻り、消費されないわけです。この回路により効率は劇的に向上します。

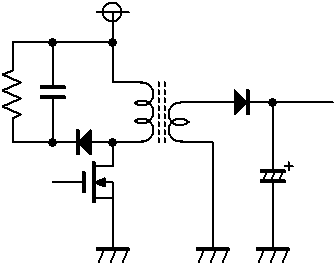

オートトランスによる昇圧回路

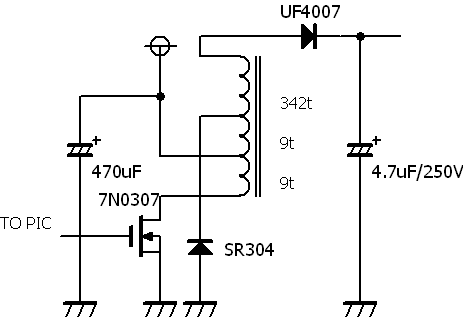

今回はニキシー管などのローカル高圧源としてオートトランス(単巻トランス)による設計を行います。基本的には前出のリセット回路を設けたコンバータそのもので、単に2次側を非絶縁にしているだけです。単巻化によって2次の巻数が少し減ります。基本回路は次の通りで、Power MOSの駆動信号はPICマイコンのPWMで発生させます。

Power MOSは手持ちの7N0307を使いました。VGS=5Vで低いON抵抗が得られる素子を選択すれば何でも良いです。Power MOSは小型SMDパッケージ品でも思いのほかIDを流せます。高圧側の整流はUF4007を使用しました。これはファーストリカバリダイオードです。リセット側のSR304は別に3A規格が必要なわけではなく、ジャンク部品の流用です。これまた高速なショットキバリアダイオードです。とにかく高速性が必要です。通常の整流ダイオードはリカバリー時間が長く、高周波では使えません。

コンデンサは出来るだけ低ESR品を使用し、トランス近くに配置します。ノイズ対策を考えると、高周波電流ループ面積が最小になるよう設計すべきです。

入手するものは、フェライトコア、ボビン、エナメル線(ウレタン線、ホルマル線)、テープです。コアとボビンはセットで入手してください。アイコー電子で売っています。この際、バンドと称する金属製の固定具がありますが、小さなトランスであれば 十分自立できるので不要です。テープはマイラーテープ、ポリエステルテープなどがもっとも良いです。オヤイデ電気においてありますので、ウレタン線等と同時に購入すれば良いでしょう。 細いウレタン線は絡まりやすいので、袋入りの小分けしたもの(すぐに絡まる)よりボビンに巻いたある程度サイズのあるものを買っておいた方が結局は得だと思います。

アイコー電子はオヤイデ向かいのラジオデパートにありますので一式そろいます。テープは透明より、黄色などのほうが使いやすいです。特に層間テープとして使う場合、透明だと下の層が見えるのでキチンと巻けているかどうか確認しづらいからです 。 可能であれば、高周波ニスなども入手しておきます。トランスができあがった後でニス漬けにすると湿気や絶縁で有利になります。

|

|

|

|

| EIコア(EI16)とボビン | ポリエステルテープ | ウレタン線 | 高周波ニス |

エナメル線の太さなのですが、あまり太いと巻けません。EI16あたりは巻枠が小さいので相当細い線でなければ回数を稼げません。かといって細すぎると損失が大きくなりますので適当なところにします。1次側のほうが電流が大きいので太くなります。ここでは1次側は0.3mm、2次側は0.1mm程度とします。

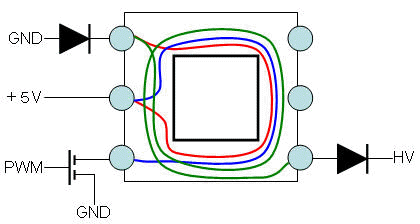

1次2次のどちらから先に巻いても良く、巻きやすいほうから巻けば良いです。

|

1次巻線 青 9回 リセット巻線 赤 9回 2次巻線 緑 342回

|

|

巻線例(TopView) |

今回のトランスは単巻トランス(オートトランス)にしますので、1次2次は絶縁していません。。青線が1次側で9回巻、赤線がリセット用の巻線で同じく9回巻、緑線は2次側として使いますが、18回巻分は共通ですので360-18の342回巻となります。

|

|

|

|

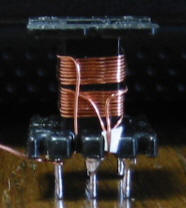

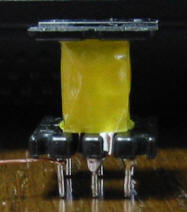

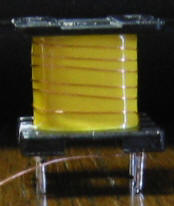

| 1次とリセット巻線 | 1次テーピング | 2次の最後の数回 | 完成 |

2次側を300回以上巻くのは結構骨が折れます。EI16のボビンはちょうど割り箸が中に通るので、割り箸を通してクルクル回して巻き取ってゆきます。2次側は電圧が大きくなっているため、絶縁に配慮しなければなりません。0.1mmの線はボビンにだいたい1層70回くらい巻けますので、2層になると最大140回ぶんの電圧が上下にかかります。これは(140/9)*5=78Vもの電位差になりますのでエナメル線の絶縁だけではこころもとなく、1層ごとにテーピングして層間絶縁します。

層間テーピングにはもう一つ理由があり、それはコイル間のストレキャパシティを減らすためでもあります。周波数が高くなるとこのキャパシティが無視できなくなってきます。

だいたい1時間もあれば製作できると思います。

インダクタンスを測定すればテーピング後でもコイルが正しく巻けているかどうか確認できます。上のインダクタンスの定義式を展開すると

となり、インダクタンスは巻数の2乗に比例します。このうち、特に巻数1の時の値をAL値といいます。

AL値は透磁率とコアの断面積、磁路長から計算できますが、たいていはコアのパラメータとして用意されています。上記の式から計算すると、1.6μHとなりますが、TDKのカタログでは1.1μHとなっています。この差は透磁率が2300ではなく、もっと小さいことを意味しています。使用した透磁率2300はカタログでは初透磁率とあります。つまり、BHグラフの0点の傾きを言っています。実際は緩やかにカーブが寝てきますので、 実際の透磁率は2300ではないということです。グラフが急速に寝てくる領域は磁気飽和 に近づいている部分です。磁気飽和に近づくと過大電流で事故になりますので避けなければなりません。

これは、μが下がる→インダクタンスが下がる→電流が増える→Hが増加する→ますますμが下がる、という正帰還が生じて急速に過大電流が流れ 、制御不能になります。なお、自励式のコンバータはこの正帰還を積極的に利用して発振しているものもあります。

少しそれましたが、製作したトランスのインダクタンス、巻数、計算したAL値の関係です。2次側の巻数は2,3回ずれている可能性があります。それほどの精度は必要なく、さほどしっかり数えていなかったので。

| 回路 | 巻数 | インダクタンス | AL値 |

| 1次 | 9 | 85.5uH | 1.06uH |

| リセット | 9 | 84.9uH | 1.05uH |

| 1次+リセット | 18 | 349uH | 1.08uH |

| 2次 | 342 | 126mH | 1.07uH |

| 1次+リセット+2次 | 360 | 132mH | 1.01uH |

計算したAL値はTDKカタログの1.1uHとだいたい一致しています。巻数はほぼあっているということです。また、重要な点として回路が直列接続された場合にインダクタンスが増加していることが上げられます。もし、コイルを逆巻きにするとインダクタンスは減少しますので、正しい方向に 巻けているという確認になります。

上記のトランスを用いて5Vを200VにステップアップするDC-DCコンバータを作ってみます。

信号源として、手持ちのPWM内蔵PIC16F88を用いました。周波数は当然ながら50kHzとします。PIC16F88はチップ内にクロック発振子を内蔵しているため、パスコン1個で動かすことができます。

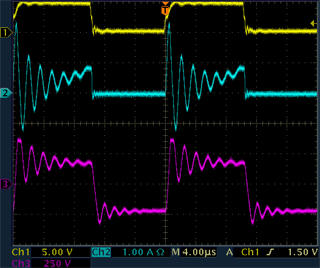

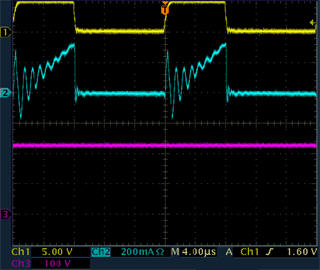

無負荷状態

入力は5V/47mA、出力は330V程度とかなり設計値とずれがあります。オシロでみると一目瞭然で、大きなリンギングが生じており、コンデンサインプット整流はそのピークホールドをしているのです。このリンギングはおそらく2次巻線のストレキャパシティとインダクタンスからくる共振です。2次のリンギング終止電圧はだいたい200Vになっているので設計と一致します。

2次ダイオードの耐圧について

紫の波形をみてもわかるようにマイナス側にも200V振っています。リンギングが無いと仮定するとダイオードにはコンデンサにチャージされた+200Vがアノードに、-200Vがカソードにかかります。従って、出力電圧の2倍の逆電圧がかかり、余裕をみて出力電圧の3倍の逆耐圧が必要で 、これは定石です。

|

CH1 黄 Power MOS VGS (5V/div) CH2 青 Power MOS ID (1A/div) CH3 紫 トランス2次電圧 (250V/div) Time (4us/div) |

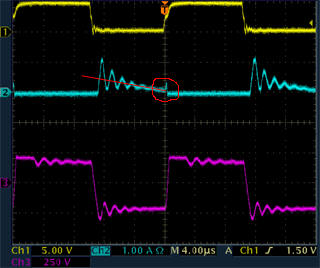

リセット回路の電流

プローブをリセット巻線につなぎ替えています。リンギングが出ていますが平均をとれば(I=-Vt/L)で減少します。ここで問題があります。波形をみると、Iが完全にゼロに戻っていません。

励磁による磁束はNVt/Lで上昇し、リセットによる磁束は回路中のダイオードのVFを加味すると、-N(V+VF)t/Lで減少します。励磁による磁束増加<リセットによる磁束減少としないと、磁束が蓄積されて磁気飽和します。磁束がゼロに戻らないというのはこの磁気飽和の一歩手前です。実はリセット回路のダイオードのVFがもっと大きいことを見込んでデューティ比0.5で設計しました。このダイオードのVFだけリセット時間が短くなるという寸法です。しかしながらショットキバリアのVFはきわめて小さく、余裕が全くないということがわかりました。テスターのダイオード測定を行うと、VFはなんと0.1V程度と僅少です。

従って、デューティ比を0.4に下げることにします。

|

CH1 黄 Power MOS VGS (5V/div) CH2 青 リセット回路電流 (1A/div) CH3 紫 トランス2次電圧 (250V/div) time (4us/div)

赤丸の中をよく見ると電流がゼロに戻っていない。 |

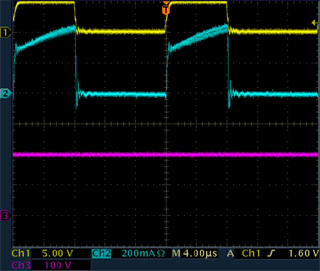

デューティ比0.4、無負荷状態

デューティ比を0.4に下げたところ、無負荷でも230V程度まで下がりました。リンギング自体はデューティ0.5の時ピーク2A程度だったものが、0.4では300mA程度と相当小さくなっています。トランスコアのエネルギが放出され切っていない状態だったことがピークが大きい原因と思われます。

|

CH1 黄 Power MOS VGS (5V/div) CH2 青 Power MOS ID (200mA/div) CH3 紫 出力電圧 (100V/div) Time (4us/div) |

100kΩ負荷状態

リンギングはほぼ無くなります。出力は200Vまで下がります。

|

CH1 黄 Power MOS VGS (5V/div) CH2 青 Power MOS ID (200mA/div) CH3 紫 出力電圧 (100V/div) Time (4us/div) |

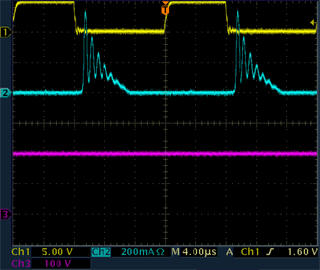

リセット回路の電流

平均43mAが電源側にリターンしています。1次巻線の平均電流が141mAであることからも、リセット回路がいかに効率化に寄与しているかがわかります。デューティを下げたため、リセット電流が確実に0になっています。

|

CH1 黄 Power MOS VGS (5V/div) CH2 青 リセット回路電流 (200mA/div) CH3 紫 出力電圧 (100V/div) Time (4us/div) |

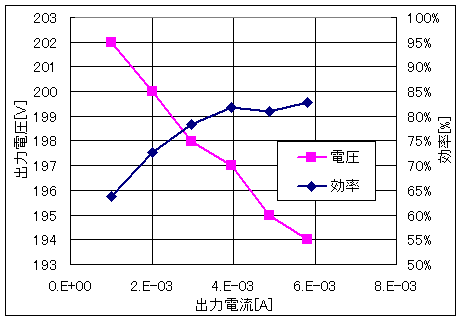

効率

一般的に効率はカマボコ特性になることが多いようです。出力が小さいうちは、発振回路などの消費電力が支配的で効率が上がりません。出力電力0でも入力は0ではないわけで、極端な例ですが、出力を取らない限り効率は0なわけです。出力を取るに従って、発振回路などの電力割合が下がり、効率は相対的に上がります。さらに電力を取ると導体損やダイオードのVFなどが効いてきて効率が若干落ちます。

今回、効率が落ちるところまではとれていないのですが、だいたいベスト値で効率80%強が得られました。このときの出力電流は5mA程度で、ニキシー用としてはここまで電流を流すことは無いと思います。ニキシー用ならだいたい1-2mAくらいかと思います。この場合は70%程度の効率が得られます。1-5mAの負荷電流変化に対し、出力電圧変化は7V程度(3.5%)の変異です。無帰還にしてはまずまずのレギュレーションだと思います。

|

[戻る]